計(jì)算機(jī)軟硬件背后的運(yùn)行機(jī)制,深植于數(shù)字邏輯電路的精妙設(shè)計(jì)之中。《編碼:隱匿在計(jì)算機(jī)軟硬件背后的語(yǔ)言》第14章深入探討了邊沿觸發(fā)器和計(jì)數(shù)器這兩個(gè)關(guān)鍵的硬件組件,它們是現(xiàn)代計(jì)算機(jī)時(shí)序控制和數(shù)據(jù)處理的基石。本章內(nèi)容精煉地揭示這些基礎(chǔ)元件如何協(xié)作,支撐起復(fù)雜的計(jì)算任務(wù)。

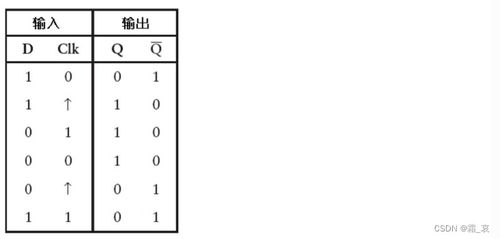

邊沿觸發(fā)器是一種時(shí)序邏輯電路,能夠在時(shí)鐘信號(hào)的特定邊沿(如上升沿或下降沿)捕獲并存儲(chǔ)輸入數(shù)據(jù)。與電平觸發(fā)的鎖存器不同,邊沿觸發(fā)器僅在時(shí)鐘邊沿瞬間響應(yīng),有效避免了競(jìng)爭(zhēng)冒險(xiǎn)和信號(hào)抖動(dòng)問題。這一特性使其在寄存器、狀態(tài)機(jī)和同步系統(tǒng)中廣泛應(yīng)用,例如作為CPU中程序計(jì)數(shù)器和狀態(tài)寄存器的基礎(chǔ)單元。其工作原理依賴于內(nèi)部交叉耦合的門電路結(jié)構(gòu),確保數(shù)據(jù)的穩(wěn)定性和可靠性。

計(jì)數(shù)器作為邊沿觸發(fā)器的直接應(yīng)用,是數(shù)字系統(tǒng)中的核心組件之一。它通過一系列觸發(fā)器級(jí)聯(lián),實(shí)現(xiàn)二進(jìn)制或十進(jìn)制計(jì)數(shù)功能,廣泛用于時(shí)鐘分頻、事件計(jì)數(shù)和地址生成等場(chǎng)景。例如,在計(jì)算機(jī)內(nèi)存管理中,計(jì)數(shù)器幫助生成順序地址;在時(shí)序控制中,它協(xié)調(diào)指令執(zhí)行周期。常見的異步計(jì)數(shù)器結(jié)構(gòu)簡(jiǎn)單但存在傳播延遲,而同步計(jì)數(shù)器通過統(tǒng)一時(shí)鐘信號(hào)提升了速度和可靠性。

邊沿觸發(fā)器和計(jì)數(shù)器的結(jié)合,不僅體現(xiàn)了硬件設(shè)計(jì)的高效性,還彰顯了計(jì)算機(jī)層級(jí)抽象的思想:從底層的邏輯門到功能模塊,最終支撐起高級(jí)軟件指令的執(zhí)行。掌握這些原理,是理解計(jì)算機(jī)如何從簡(jiǎn)單脈沖邁向復(fù)雜運(yùn)算的關(guān)鍵一步。